NXP S32K344: Unstable or not working parallel trace

By default the fast internal RC oscillator (FIRC) is used for generating the trace clock. The resistor and capacitor values (RC components) of this oscillator show significant tolerances due to the nature of the manufacturing process and also vary upon differences in supplied voltage and working temperature. The resulting trace clock frequency can vary to such an extent that it causes bit errors in the trace messages which the trace analyzer can no longer properly decode.

Possible solutions

Reduce the frequency of the trace clock

Reducing the trace clock frequency makes the trace recording less susceptible to errors caused by frequency variations.

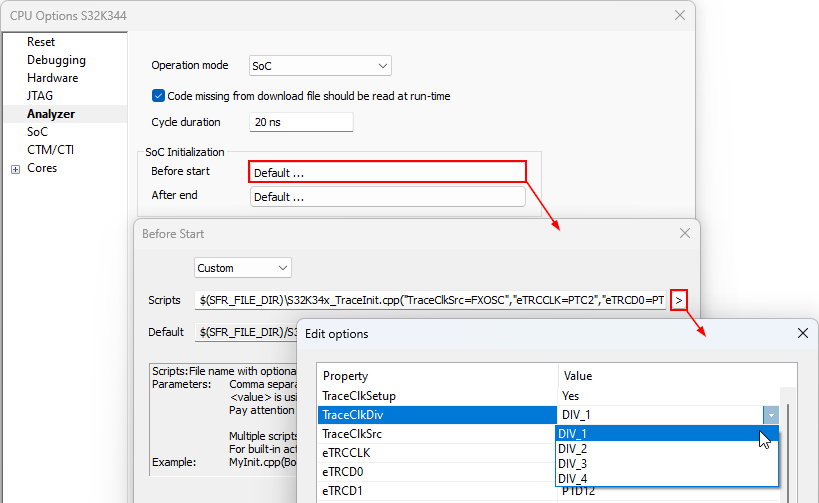

1. Add the custom script S32K34x_TraceInit.cpp to Hardware | CPU Options | Analyzer | SoC Initialization.

2. Select a higher value for the TraceClkDiv property in the initialization script parameters.

3. Restart the debug session and perform a Trace Line Calibration before running the Analyzer.

Select an external clock as the trace clock source

If the first solution doesn't provide the required trace bandwidth, the source of the trace clock needs to be switched to a more stable external clock (FXOSC).

1. Initialize the FXOSC and PLL's in your application and set up either PHI0 or PHI1 as the trace clock source.

2. Change TraceClkSrc accordingly in the initialization script parameters.

3. Restart the debug session and perform a Trace Line Calibration.

More resources in winIDEA Help

Same category topics

- Renesas RH850: Software Trace (SFT) FIFO Overflows

- winIDEA Infineon AURIX: Find two or more problematic functions in a wider range if AGBT FIFO has overflowed

- Arm Cortex-M: How to manually configure DWT Data Comparator 1?

- Infineon AURIX: Find a problematic function in a narrow range if AGBT FIFO overflowed?

- How to measure Core / CPU Load?

Similar topics

- NXP S32K31x: Trace recording is incomplete and it shows synchronization errors

- Arm Cortex: Parallel trace doesn't work after switching applications

- Trace not working after applying the recommended calibration values

- NXP S32Kxx: Programming Flash memory not possible

- winIDEA: Configuring JTAG Scan speed