Arm Cortex Cypress Traveo II: Emulation Adapters

Cypress Traveo II packages (64-pin, 80-pin, 100-pin, and 144-pin) have different trace capabilities. The following Emulation Adapters provide the trace interfaces, where a trace port is not available or lacks the full trace capability:

By default, port pins P18 (P18_3 – P18_7), and P22 (P22_0 – P22_4) are set as GPIO pins, but TRACE CLOCK and TRACE DATAn signals can be allocated to either.

It’s also possible to mix these signals across both ports randomly. For example:

- TRACE CLOCK, TRACE DATA1, TRACE DATA3 signals on P18

- TRACE DATA0, TRACE DATA2 on P22

Possible solution

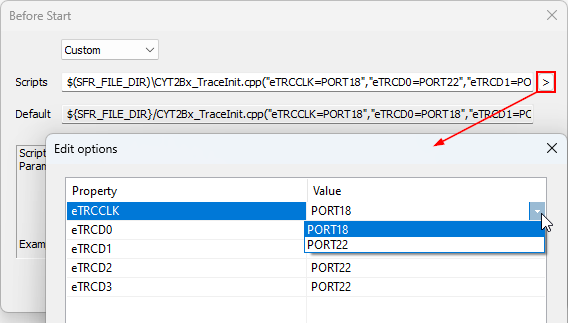

1. Add the custom script CYT2Bx_TraceInit.cpp to Hardware | CPU Options | Analyzer | SoC Initialization.

2. Depending on the target board configuration, edit the script parameters and allocate:

- TRACE CLOCK Port to PORT 18 (or PORT 22)

- TRACE DATAn PORT to PORT 18 (or PORT 22)

4. Go to Hardware | CPU Options | SoC and enable 2, 3 for Trace Trigger and Flush in Use Cross Trigger Channels.