NXP S32K31x: Trace recording is incomplete and it shows synchronization errors

Trace recording is incomplete because of the big gaps in time and trace message number, with ITM Synchronization lost messages in between. This typically happens due to the SWO clock instability, or too high of SWO data rate.

Possible solution

1. Update to the latest winIDEA version.

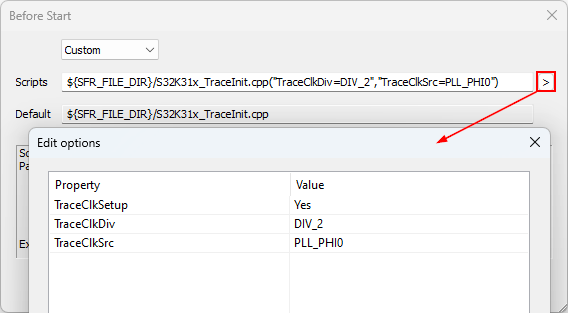

2. Add a custom S32K31x_TraceInit.cpp script via Hardware | CPU Options | Analyzer | SoC Initialization Before Start.

3. Configure the script to use a more stable clock source for the SWO module.

4. Configure the MUX divider (TraceClkDiv) parameter for the script.

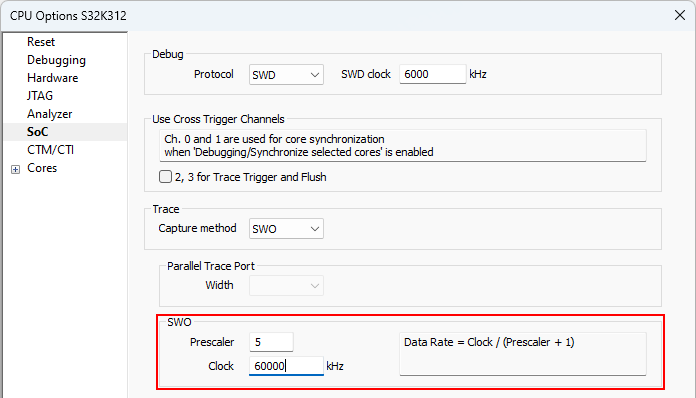

5. Configure the Prescaler value in Hardware | CPU Options | SoC to aim for a SWO data rate that allows stable trace data capture.

6. (optional) If you continue experiencing synchronization of lost messages, try reducing the data rate by reconfiguring the MUX divider and SWO Prescaler.

Explanation

MUX divider

Typically SWO pin is connected to the TPIU, and on most Cortex-M devices TPIU clock is derived 1/1 from the CPU clock. However, the S32K31x devices have a SWO module (not a TPIU with SWO functionality but a separate SWO module). The TRACE_CLK, which is fed into the SWO module, is derived by a separate clock MUX, which selects the clock and prescales it according to the values of its configuration registers.

The default clock source for TRACE_CLK is FIRC (internal RC oscillator)

which is inherently unstable, and it causes problems in reliability of SWO

trace data capture. For this reason, a separate script is implemented for the S32K31x devices, which performs MUX

configuration as per the specified parameters, e.g. selection of the clock

source and the divider.

The clock source derived from the MUX (TRACE_CLK) is fed into the SWO module, and then additionally scaled down by the clock Prescaler in the SWO module (divisor = Prescaler +1).

Preferably it would be better to use FXOSC or the PLL clock (which is driven by FXOSC) - e.g. if the PLL_PHI0_CLK is configured by the application to be the clock source for the CPU, you can also derive the TRACE_CLK from it by configuring this via Hardware | CPU Options | Analyzer | Before Start script.

Prescaler

Additional configuration, which is general for Cortex-Mx devices featuring a SWO module (this is a part of the CoreSight component) is the Prescaler setting found in Hardware | CPU Options | SoC. In general, the Clock parameter is where you would write the CPU clock because the SWO clock is typically derived 1/1 from CPU clock, but in this case, we would write the TRACE_CLK value, since this is specific for this device.

Example

In this example, it is assumed that PLL_PHI0 is enabled and configured as PLL_PHI0_clk = 120 MHz.

S32K31x_TraceInit.cpp script parameters:

- TraceClkSetup : Yes

- TraceClkDiv = 2

- TraceClkSrc : PLL_PHI0

-

TRACE_CLK = PLL_PHI0_clk / TraceClkDiv = 60 MHz.

TRACE_CLK is fed into the SWO module, where we configured the

Prescaler to value 5.

Therefore:

SWO_dataRate = TRACE_CLK / (Prescaler + 1) = 10 Mbit